# Semester I

Estd.

Discipline: ELECTRONICS &

COMMUNICATION

**ENGINEERING**

Stream: EC8

| CODE      | COURSE NAME                            | CATEGORY           | L | T | P | CREDIT |

|-----------|----------------------------------------|--------------------|---|---|---|--------|

| 221TEC100 | ADVANCED<br>ENGINEERING<br>MATHEMATICS | DISCIPLINE<br>CORE | 3 | 0 | 0 | 3      |

**Preamble:** The purpose of this course is to expose students to the basic theory of linear algebra and probability.

**Course Outcomes:** The COs shown are only indicative. For each course, there can be 4 to 6 COs. After the completion of the course the student will be able to

| CO 1 | To analyze distributions of random variables and make computations based on that                              |  |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CO 2 | evaluate average behaviour of random variables, and analyze their converging behviours                        |  |  |  |  |  |  |

| CO 3 | To analyze behaviour of random processes and explain basis of vector spaces.                                  |  |  |  |  |  |  |

| CO 4 | To evaluate properties of linear transformations                                                              |  |  |  |  |  |  |

| CO 5 | To evaluate if a linear tranformaion is diagonalizable and decompose it using spectral decomposition theorem. |  |  |  |  |  |  |

#### Mapping of course outcomes with program outcomes

|      | PO 1 | PO 2 | PO 3 | PO4   | PO5 | PO6 | PO7 |

|------|------|------|------|-------|-----|-----|-----|

| CO 1 | 3    |      | 3    |       | 3   | 3   |     |

| CO 2 | 3    |      | 3    |       | 3   | 3   |     |

| CO 3 | 3    |      | 3    |       | 3   | 3   |     |

| CO 4 | 3    |      | 3 E  | · d   | 3   | 3   |     |

| CO 5 | 3    |      | 3    | .G. 1 | 3   | 3   |     |

#### **Assessment Pattern**

| Bloom's Category | End Semester Examination |

|------------------|--------------------------|

| Apply            | 20                       |

| Analyse          | 20                       |

| Evaluate         | 20                       |

| Create           |                          |

#### Mark distribution

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|

| 100         | 40  | 60  | 2.5 hours    |

#### **Continuous Internal Evaluation Pattern:**

Continuous Internal Evaluation: 40 marks

- Problem assignments including unsolved exercise problems from reference text books: 20 marks

- Quiz: 10 marks

- Test paper (1 number): 10 marks

Quiz shall include topics from at least 50% of the syllabus. Test paper shall include minimum 80% of the syllabus

#### **End Semester Examination Pattern:**

End Semester Examination: 60 marks

There will be two parts; Part A and Part B

- Part A will contain 5 numerical/short answer questions with 1 question from each module, having 5 marks for each question. Students should answer all questions.

- Part B will contain 7 questions with minimum one question from each module of which student should answer any five. Each question can carry 7 marks.

#### **Model Question paper**

## A P J ABDUL KALAM TECHNOLOGICAL UNIVERSITY M.TECH DEGREE EXAMINATION SEMESTER:

#### **Branch:**

#### ADVANCED ENGINEERING MATHEMATICS

Time: 2.5 Hours Marks: 60

#### Part A

#### Answer ALL Questions. Each question carries 5 marks

- 1. Given that  $f(x) = \frac{k}{2^x}$  is a probability distribution of a random variable that can take on the values  $x = 0,1,2,3,\land 4$ . Find k. Find the cumulative distribution function.

- 2. State and prove weak law of large numbers.

- 3. Show that (1,3,2,-2), (4,1,-1,3), (1,1,2,0), (0,0,0,1) is a basis for  $\mathbb{R}^4$ .

- 4. Let  $T: V \to W$  be a linear transformation defined by T(x, y, z) = (x + y, x y, 2x + z). Find the range, null space, rank and nullity of T.

- 5. Describe an inner product space. If V is an inner product space, then for any vectors  $\alpha, \beta$  in V prove that  $\|\alpha + \beta\| \le \|\alpha\| + \|\beta\|$ .

#### Part B

## Answer ANY FIVE Questions, one from each module (5 x 7 marks = 35marks)

- 6. If the probability mass function of a RV X is given by  $P(X = x) = kx^3$ , x = 1,2,3,4. Find the value of k,  $P\left[\left(\frac{1}{2} < X < \frac{3}{2}\right)/X > 1\right]$ , mean and variance of X.

- 7. If the moment generating function of a uniform distribution for a random variable X is  $\frac{1}{t}(e^{5t}-e^{4t})$ . Find E(X).

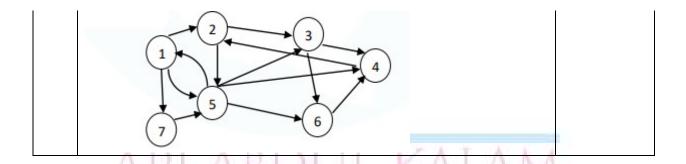

- 8. Consider the Markov chain with three states, s={1,2,3} that has the following

transition matrix

$$P = \begin{bmatrix} \frac{1}{2} & \frac{1}{4} & \frac{1}{4} \\ \frac{1}{3} & 0 & \frac{2}{3} \\ \frac{1}{2} & \frac{1}{2} & 0 \end{bmatrix}$$

Draw the state diagram for the chain. If  $P(X_1 =$

1) =

$$P(X_2 = 2) = \frac{1}{4}$$

, find  $P(X_1 = 3, X_2 = 2, X_3 = 1)$ .

9. Find the eigen values and eigen vectors of

$$A = \begin{bmatrix} 2 & 2 & 1 \\ 1 & 3 & 1 \\ 1 & 2 & 2 \end{bmatrix}$$

.

- 10. Find the least square solution to the equation Ax = b, where  $A = \begin{bmatrix} 1 & 2 \\ 1 & 3 \\ 0 & 0 \end{bmatrix}$  and  $b = \begin{bmatrix} 1 & 2 \\ 1 & 3 \\ 0 & 0 \end{bmatrix}$

- Obtain the projection matrix P which projects b on to the column space of A.

- 11.Let T be the linear transformation from  $R^3$  to  $R^2$  defined by T(x,y,z) = (x+y, 2z-x). Let  $B_1$ ,  $B_2$  be standard ordered bases of  $R^3$  and  $R^2$  respectively. Compute the matrix of T relative to the pair  $B_1$ ,  $B_2$ .

- 12.Let V be a finite-dimensional complex inner product space, and let T be any linear operator on V. Show that there is an orthonormal basis for V in which the matrix of T is upper triangular.

#### **Syllabus**

**Module 1** Axiomatic definition of probability. Independence. Bayes' theorem and applications. Random variables. Cumulative distribution function, Probability Mass Function, Probability Density function, Conditional and Joint Distributions and densities, Independence of random variables. Functions of Random Variables: Two functions of two random variables. Pdf of functions of random variables using Jacobian.

**Module 2** Expectation, Fundamental theorem of expectation, Moment generating functions, Characteristic function. Conditional expectation. Covariance matrix. Uncorrelated random variables. Pdf of Jointly Gaussian random variables, Markov and Chebyshev inequalities, Chernoff bound. Central Limit theorem. Convergence of random variables. Weak law of large numbers, Strong law of large numbers.

**Module 3** Random Processes. Poisson Process, Wiener Process, Markov Process, Birth-Death Markov Chains, Chapman-Kolmogorov Equations,

Groups, Rings, homomorphism of rings. Field. Vector Space. Subspaces. direct sum. Linear independence, span. Basis. Dimension. Finite dimensional vector spaces. Coordinate representation of vectors. Row spaces and column spaces of matrices.

Module 4 Linear Transformations. Four fundamental subspaces of a linear transformation. Rank and Rank-nullity theorem. Matrix representation of linear transformation. Change of basis transformation. System of linear equations. Existence and uniqueness of solutions. Linear functionals. Dual, double dual and transpose of a linear transformation.

Module 5 Eigen values, Eigen vectors, Diagonizability.

Inner product. Norm. Projection. Least-squares solution. Cauchy-Schwartz inequality. Orthonormal bases. Orthogonal complement. Spectral decomposition theorem.

#### **Course Plan**

| No  | Topic                                                                                                                      | No. of<br>Lectures |  |

|-----|----------------------------------------------------------------------------------------------------------------------------|--------------------|--|

|     | Module I                                                                                                                   |                    |  |

| 1.1 | Axiomatic definition of probability. Independence. Bayes' theorem and applications.                                        | 2                  |  |

| 1.2 | Random variables. Cumulative distribution function, Probability Mass Function,                                             | V1<br>1            |  |

| 1.3 | Probability Density function, Conditional and Joint Distributions and densities, Independence of random variables.         | 2                  |  |

| 1.4 | Functions of Random Variables: Two functions of two random variables. Pdf of functions of random variables using jacobian. | 2                  |  |

|     | Module II                                                                                                                  |                    |  |

| 2.1 | Expectation, Fundamental theorem of expectation, Conditional expectation.                                                  | 1                  |  |

| 2.2 | Moment generating functions, Charectristic function.                                                                       | 1                  |  |

| 2.3 | Covariance matrix. Uncorrelated random variables. Pdf of Jointly Guassian random variables,                                | 2                  |  |

| 2.4 | Markov and Chebyshev inequalities, Chernoff bound. Central Limit theorem.                                                  | 2                  |  |

| 2.5 | Convergence of random variables. Weak law of large numbers, Strong law of large numbers.                                   | 2                  |  |

| 3   | Module III                                                                                                                 |                    |  |

| 3.1 | Random Processes. Poisson Process, Wiener Process,                                                                         | 2                  |  |

| 3.2 | Markov Process, Birth-Death Markov Chains, Chapman-Kolmogorov Equations,                                                   | 2                  |  |

| 3.3 | Groups, Rings, homomorphism of rings. Field. Vector Space. Subspaces. direct sum.                                          | 2                  |  |

| 3.4 | Linear independence, span. Basis. Dimension. Finite dimensional vector spaces.                                             | 2                  |  |

| 3.5 | Coordinate representation of vectors. Rowspaces and column spaces of matrices.                                             |                    |  |

| 4   | Module IV                                                                                                                  | -                  |  |

| 4.1 | Linear Transformations. Four fundamental subspaces of a linear transformation. Rank and Rank-nullity theorem.              | 2                  |  |

| 4.2 | Matrix representation of linear transformation. Change of basis transformation.                                            |                    |  |

| 4.3 | System of linear equations. Existence and uniqueness of solutions.                                                         | 2                  |  |

| 4.4 | Linear functionals. Dual, double dual and transpose of a linear transformation.                                            | 2                  |  |

| 5   | Module V                                                                             |   |

|-----|--------------------------------------------------------------------------------------|---|

| 5.1 | Eigen values, Eigen vectors, Diagonizability.                                        | 2 |

| 5.2 | Inner product. Norm. Projection. Least-squares solution. Cauchy-Schwartz inequality. | 2 |

| 5.3 | Orthonormal bases. Orthogonal complement. Spectral decomposition theorem.            | 2 |

#### **Reference Books**

- 1. Hoffman Kenneth and Kunze Ray, Linear Algebra, Prentice Hall of India.

- 2. Jimmie Gilbert and Linda Gilbert, Linear Algebra and Matrix Theory, Elsevier

- 3. Henry Stark and John W. Woods "Probability and Random Processes with Applications to Signal Processing", Pearson Education, Third edition.

- 4. Athanasios Papoulis and S. Unnikrishna Pillai. Probability, Random Variables and Stochastic Processes, TMH

| CODE      | COURSE NAME         | CATEGORY        | L | T | P | CREDIT |

|-----------|---------------------|-----------------|---|---|---|--------|

| 221TEC001 | SYSTEM DESIGN USING | Program<br>Core | 3 | 0 | 0 | 3      |

|           | EMBEDDED PROCESSORS | Core            |   |   |   |        |

**Preamble:** Embedded systems are normally built around Microcontrollers and ARM Processor based SoCs. This Embedded System using Embedded Processors course focuses on the architecture and programming of embedded processors. The objective of the course is to provide understanding of the techniques essential to the design and implementation of embedded systems using suitable hardware and software tools. This course offers a range of topics of immediate relevance to industry and makes the participants exactly suitable for Embedded Industry

**Course Outcomes:** The COs shown are only indicative. For each course, there can be 4 to 6 COs.

After the completion of the course the student will be able to

| CO 1 | Comprehend Embedded Processor and its software                          |

|------|-------------------------------------------------------------------------|

| CO 2 | Design an Embedded system with ARM microcontrollers                     |

| CO 3 | Design an Embedded system using processors, memory I/O devices          |

|      | and communication network within realistic constraints.                 |

| CO 4 | Comprehend ARM Cortex M4 microcontrollers                               |

| CO 5 | Comprehend the peripheral programming of ARm cortex M4 Microcontrollers |

| CO 6 | Comprehend advanced Embedded Controllers, Features and case studies     |

#### Mapping of course outcomes with program outcomes

|      | PO 1 | PO 2 | PO 3 | PO 4 | PO 5 | PO 6 | PO 7 |

|------|------|------|------|------|------|------|------|

| CO 1 | 1    | 1    | -    | 3    |      | -    | -    |

| CO 2 | -    | -    | -    | -    | 1    | 2    | -    |

| CO 3 | -    | -    | 2    | -    | 2    | -    | -    |

| CO 4 | -    | -    | 3    |      | 2    | -    | -    |

| CO 5 | 2    | -    | -    | 3    | _    | -    | _    |

| CO 6 | 2    | -    | -    | 3    | -    | -    | -    |

#### **Assessment Pattern**

| Bloom's Category | End Semester |

|------------------|--------------|

|                  | Examination  |

| Apply            | 20           |

| Analyse          | 20           |

| Evaluate         | 10           |

| Create           | 10           |

#### Mark distribution

| Total<br>Marks | CIE | ESE | ESE<br>Duration |

|----------------|-----|-----|-----------------|

| 100            | 40  | 60  | 2.5 hours       |

#### **Continuous Internal Evaluation Pattern: 40 Marks**

Micro project/Course based project: 20 marks Course based task/Seminar/Quiz: 10 marks

Test paper, 1 no.: 10 marks

The project shall be done individually. Group projects not permitted. Test paper shall include minimum 80% of the syllabus.

#### **End Semester Examination Pattern: 60 Marks**

The end semester examination will be conducted by the University. There will be two parts; Part A and Part B. Part A will contain 5 numerical/short answer questions with 1 question from each module, having 5 marks for each question (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students). Students should answer all questions. Part B will contain 7 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student should answer any five. Each question can carry 7 marks. Total duration of the examination will be 150 minutes.

#### **Model Question paper**

## APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY MONTH & YEAR

| Course Code: 221TEC001 |                                                                        | Course Name: PROCESSORS                                  | SYSTEM DESIGN                                                             | USING EM                 | BEDDED     |

|------------------------|------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------|--------------------------|------------|

| Tin                    | me : 2.5 Hours                                                         | ABDL                                                     | JL KAL                                                                    | Maximum                  | : 60 Marks |

|                        | PAI                                                                    | RT A (Answer all                                         | questions)                                                                | JAL                      |            |

| 1                      | How do we classift of applications?                                    |                                                          | systems based on c<br>ry with examples.                                   | omplexity                | 5 marks    |

| 2                      | Discuss the Interest<br>Microcontroller                                | connect Matrix co                                        | ncepts in ARM Cor                                                         | tex M4                   | 5 marks    |

| 3                      | Discuss the usage examples.                                            | e of the Watchdog                                        | timer with suitabl                                                        | e                        | 5 marks    |

| 4                      | Discuss how to er based application                                    |                                                          | ncryption Standard<br>tex M4.                                             | i (AES)                  | 5 marks    |

| 5                      | Write a short note<br>Computing techni                                 |                                                          | g for Power-Efficien                                                      | t                        | 5 marks    |

|                        | PAR1                                                                   | B (Answer any                                            | 5 questions)                                                              |                          |            |

| 6.                     | _                                                                      | ontrast ARM, Thu<br>architecture in Al                   | umb, and Thumb-2<br>RM processors.                                        |                          | 7 marks    |

| 7                      | Discuss the AM                                                         | IBA and AXI bus.                                         | td                                                                        |                          | 7 marks    |

| 8.                     | 1                                                                      | olock diagram exp<br>Microcontroller.                    | plain the architectu                                                      | re of                    | 7 marks    |

| 9.                     | Explain the wor                                                        | rking of NVIC on .                                       | ARM Cortex M4.                                                            |                          | 7 marks    |

| 10                     | with the followi<br>Microcontroller<br>and Blue & Gre<br>respectively. | ng events in emb<br>. Assume that ini<br>en LEDs are con | implement an appedded C on Cortex tially both LEDs ar nected to Ports PB6 | M4<br>e OFF<br>5 and PB7 | 7 marks    |

|                        | ii. Switch                                                             | h ON the Green L                                         | ED once character                                                         | 'A' is                   |            |

|     | received                                                                   |         |

|-----|----------------------------------------------------------------------------|---------|

|     | iii. Switch OFF Green LED on receiving 'B'.                                |         |

|     | iv. Switch ON Blue LED the once character 'C' is                           |         |

|     | received Switch OFF Blue LED on receiving 'D'.                             |         |

| 11. | Write a short note on                                                      | 7 marks |

|     | i. Quad SPI in ARM cortex M4                                               |         |

|     | ii. Memory protections                                                     |         |

| 12. | Design a real-time data acquisition system using ARM                       | 7 marks |

|     | Cortex M4 Microcontroller. It is required to periodically                  |         |

|     | monitor and control the temperature in a boiler which                      |         |

|     | ranges from 0°C to 140°C. The temperature has to be kept                   |         |

|     | at a set-point of 60°C ± 5°C. Pro <mark>vi</mark> sion should be given for |         |

|     | receiving the set-point value of temperature from the PC.                  |         |

|     | Illustrate the design with appropriate block diagrams and                  |         |

|     | flowcharts.                                                                |         |

#### **Syllabus**

#### **Module 1: Introduction to Embedded Systems**

Overview of embedded system architecture, Development and debugging Tools for Embedded Systems, Overview ARM Architecture - Architecture Versions, Instruction Set Development, Thumb-2 and Instruction Set Architecture, AMBA, AXI bus overview. Overview of the Arm Cortex-Mx Processor Architectures.

#### Module2: ARM Cortex M4 Microcontroller system

ARM Cortex M4 Core, Interconnect Matrix in ARM Cortex M4 Microcontroller, System configuration Controller, NVIC, External Interrupt Controllers, DMA, Reset and Clock Control, Clock Recovery System, Power Control.

#### Module3: ARM Cortex M4 Microcontroller Peripheral Overview

ARM Cortex M4 Core, Interconnect Matrix in ARM Cortex M4 Microcontroller, System configuration Controller, NVIC, External Interrupt Controllers, DMA, Reset and Clock Control, Clock Recovery System, Power Control.

Module4: Memory, Safety and Security in ARM Cortex Microcontroller Flash, Quad SPI Interface, Flexible Memory controller, CRC, Random Number Generator, memory protections, Advanced Encryption Standard HW Accelerator (AES), Safety support.

#### Module5: Advanced Embedded Controllers, Features and case studies

Programming for Power-Efficient Computing - High Level and low level Techniques, Cortex M7, M23 and M33 Controllers and Features, Overview of mbed platform, Embedded Systems case studies - Consumer, Medical, Automotive.

**Course Plan** (For 3 credit courses, the content can be for 40 hrs and for 2 credit courses, the content can be for 26 hrs. The audit course in the third semester can have content for 30 hours).

|     | ADIADITI VALAM                                                                  | Lectures |

|-----|---------------------------------------------------------------------------------|----------|

| 1   | Introduction to Embedded Systems                                                |          |

| 1.1 | Overview of embedded system architecture,                                       | 1        |

| 1.2 | Development and debugging Tools for Embedded Systems                            | 1        |

| 1.3 | Overview ARM Architecture - Architecture Versions,                              | 3        |

|     | Instruction Set Development, Thumb-2 and Instruction Set                        |          |

|     | Architecture,                                                                   |          |

| 1.4 | AMBA,AXI bus overview.                                                          | 2        |

| 1.5 | Overview of the Arm Cortex-Mx Processor Architectures                           | 2        |

| 2   | ARM Cortex M4 Microcontroller system                                            |          |

| 2.1 | ARM Cortex M4 Core, Interconnect Matrix in ARM Cortex                           | 3        |

|     | M4 Microcontroller                                                              |          |

| 2.2 | System configuration Controller, NVIC, External Interrupt                       | 3        |

|     | Controllers, DMA                                                                |          |

| 2.3 | Reset and Clock Control, Clock Recovery System, Power                           | 2        |

|     | Control                                                                         |          |

| 3   | ARM Cortex M4 Microcontroller Peripheral Overview                               |          |

| 3.1 | Introduction to Arm Cortex-M4 Programming, overview of                          | 1        |

|     | CMSIS                                                                           |          |

| 3.2 | GPIO, ADC, DAC                                                                  | 3        |

| 3.3 | Communication & Peripherals - USART, UART, I2C, SPI, USB, CAN                   | 3        |

| 3.4 | Watchdogs and Timers, PWM                                                       | 3        |

| 4   | Memory, Safety and Security in ARM Cortex Microcontro                           | oller    |

| 4.1 | Flash, Quad SPI Interface, Flexible Memory controller                           | 3        |

| 4.2 | CRC, Random Number Generator, memory protections                                | 3        |

| 4.3 | Advanced Encryption Standard HW Accelerator (AES),                              | 2        |

|     | Safety support                                                                  |          |

| 5   | Advanced Embedded Controllers, Features and case stud                           | ies      |

| 5.1 | Programming for Power-Efficient Computing - High Level and low level Techniques | 2        |

| 5.2 | Cortex M7, M23 and M33 Controllers and Features                                 | 1        |

| 5.3 | Overview of mbed platform                                                       | 1        |

| 5.4 | Embedded Systems case studies - Consumer, Medical,                              | 2        |

|     | Automotive                                                                      |          |

#### **Text Books**

- 1. Yiu J. The Definitive Guide to ARM Cortex M3 and Cortex M4 Processors, 3rd Edition, Elsevier

- 2. Andrew N Sloss, Dominic Symes, Chris Wright, "ARM System Developer's Guide Designing and Optimizing System Software", 2006, Elsevier.

#### Reference Books

- 1. Steve Furber, "ARM System-on-Chip Architecture", 2nd Edition, Pearson Education

- 2. Cortex-M4 Technical Reference Manual (TRM)

- 3. Raj Kamal, "Microcontroller Architecture Programming Interfacing and System Design" 1st Edition, Pearson Education

- 4. P.S Manoharan, P.S. Kannan, "Microcontroller based System Design", 1st Edition, Scitech Publications

| CODE      | COURSE NAME       | CATEGORY     | L | T | P | CREDIT |

|-----------|-------------------|--------------|---|---|---|--------|

| 221TEC012 |                   | Program Core | 3 | 0 | 0 | 3      |

|           | <b>ELECTRONIC</b> |              |   |   |   |        |

|           | SYSTEM DESIGN     |              |   |   |   |        |

#### Preamble:

The objective of this course is to make students understand, practice Design process Protection requirement and to make them capable of independently designing complex systems. The main thrust of Electronic System Design is addressing ways to "tame" the physical effects and control the unwanted side effects of the large-scale integration. The objective is to make the system reliable in production and use, and to make it resilient against external influences.

**Course Outcomes:** The COs shown are only indicative. For each course, there can be 4 to 6 COs.

After the completion of the course the student will be able to

| CO 1 | Learn Design Process and Its Fundamentals                         |  |  |  |

|------|-------------------------------------------------------------------|--|--|--|

|      | Attain comprehensive understanding of Design Process and its      |  |  |  |

|      | fundamentals.                                                     |  |  |  |

|      | (Cognitive knowledge level: <mark>U</mark> nderstand)             |  |  |  |

| CO 2 | Attain comprehensive understanding of System Architecture and     |  |  |  |

|      | Protection Requirements                                           |  |  |  |

|      | (Cognitive knowledge level: Understand).                          |  |  |  |

| CO 3 | Attain understanding in Reliability Analysis (Cognitive knowledge |  |  |  |

|      | levels: Understand, analyse, &create).                            |  |  |  |

| CO 4 | Attain understanding in designing and analysing Thermal           |  |  |  |

|      | Management and Cooling of electronic product (Cognitive           |  |  |  |

|      | knowledge levels: Understand, analyse, and create). Learn how     |  |  |  |

|      | Thermal Management and Cooling is done                            |  |  |  |

| CO 5 | Enable design of Product that meets the requirement of            |  |  |  |

|      | Electromagnetic Compatibility (EMC) (Cognitive knowledge levels:  |  |  |  |

|      | Understand, analyse, create & Evaluate).                          |  |  |  |

#### Mapping of course outcomes with program outcomes

|      | PO 1 | PO 2 | PO 3 | PO 4 | PO 5 |

|------|------|------|------|------|------|

| CO 1 | 3    | -    | _    | _    | -    |

| CO 2 | -    | 3    | -    | -    | -    |

| CO 3 | 2    | -    | -    | -    | 3    |

| CO 4 | -    | 3    | 3    | 3    | _    |

| CO 5 | -    | _    | -    | -    | 3    |

#### **Assessment Pattern**

| Bloom's Category | End Semester<br>Examination |  |

|------------------|-----------------------------|--|

| Apply            | 30                          |  |

| Analyse          | 30                          |  |

| Evaluate         | 30                          |  |

| Create           | 10                          |  |

#### Mark distribution

| Total<br>Marks | CIE | ESE | ESE<br>Duration  |

|----------------|-----|-----|------------------|

| 100            | 40  | 60  | 2Hr 30<br>minute |

#### **Continuous Internal Evaluation Pattern: 40 Marks**

Preparing a review article based on peer reviewed original publications (minimum 10 publications shall be referred) : **15 marks**

Course based task/Seminar/Data collection and interpretation: 15 marks

Test paper, 1 number: 10 marks

Test paper shall include minimum 80% of the syllabus.

#### **End Semester Examination Pattern: 60 Marks**

The end semester examination will be conducted by the University. There will be two parts; Part A and Part B. Part A will contain 5 numerical/short answer questions with 1 question from each module, having 5 marks for each question (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students). Students should answer all questions. Part B will contain 10 questions (such questions shall be useful in the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student should answer any five. Each question can carry 7 marks. Total duration of examination will be 150 minutes.

#### **Model Question paper**

| U        | Slot [SLOT] |

|----------|-------------|

| Reg. No: | Name:       |

## APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY FIRST SEMESTER M.TECH DEGREE EXAMINATION

| Subject: ELECTRONIC SYSTEM DESIGN 221EEC006                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| V V L L V V C C V C C V C V C V C V C V                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| nute                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| PART A (Answer all questions)                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| With proper depiction illustrate the Electronic System Design<br>Process for a Mobile Phone                                                                                                                                                                                                                                           | 5 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| With a suitable example detail the techniques to avoid Electronic component Failure                                                                                                                                                                                                                                                   | 5 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| What are thermal management products?                                                                                                                                                                                                                                                                                                 | 5 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Detail the techniques to avoid noise generation and counling                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| mechanisms in electronic systems                                                                                                                                                                                                                                                                                                      | marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Describe in detail the product recycling and its advantages.                                                                                                                                                                                                                                                                          | 5 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| PART B (Answer any five questions)                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Prepare a feasibility study report involved during product planning.                                                                                                                                                                                                                                                                  | 7 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Suppose 10 devices are tested for 500 hours. During the test 2                                                                                                                                                                                                                                                                        | 7 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| failures occur.                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Estimate of the MTBF and failure rate.                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| What are the most common electronic components that fail?                                                                                                                                                                                                                                                                             | 7 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Detail the various protection schemes.                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Select a Heat Sink for TO-220 package outline device is dissipating 7 watts (Q), The Maximum Junction Temperature, is Tj = 125°C, and the Maximum Ambient Temperature, is Ta = 65°C, Component Junction-to-Case Thermal Resistance, is Rθjc = 2.5 °C/W, Assuming that:  • Interface material is Silicon Grease – Wakefield 120 Series | 7 marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| ,                                                                                                                                                                                                                                                                                                                                     | PART A (Answer all questions)  With proper depiction illustrate the Electronic System Design Process for a Mobile Phone  With a suitable example detail the techniques to avoid Electronic component Failure  What are thermal management products?  Detail the techniques to avoid noise generation and coupling mechanisms in electronic systems  Describe in detail the product recycling and its advantages.  PART B (Answer any five questions)  Prepare a feasibility study report involved during product planning.  Suppose 10 devices are tested for 500 hours. During the test 2 failures occur.  Estimate of the MTBF and failure rate.  What are the most common electronic components that fail?  Detail the various protection schemes.  Select a Heat Sink for TO-220 package outline device is dissipating 7 watts (Q), The Maximum Junction Temperature, is Tight = 125°C, and the Maximum Ambient Temperature, is Ta = 65°C, Component Junction-to-Case Thermal Resistance, is R0jc = 2.5 °C/W, Assuming that: |  |  |  |  |

|    | found to be as:<br>Thermal Resistivity, ( $\rho$ ), (120 Series = 56 C-in/W), thickness, (t), (in) and contact<br>area, (A), (in^2) |         |

|----|-------------------------------------------------------------------------------------------------------------------------------------|---------|

| 10 | With proper depiction illustrate the thermal management in                                                                          | 7 marks |

|    | electronic circuitry?                                                                                                               |         |

| 11 | Analyze various aspects of noise coupling and power integrity in                                                                    | 7 marks |

|    | integrated circuits?                                                                                                                |         |

| 12 | What are the 5 steps of the recycling process? Illustrate the                                                                       | 7 marks |

|    | recycling process with an example.                                                                                                  |         |

The syllabus address the architecture and fundamental structure of the design process of electronic systems and different ways to "tame" the physical effects and control the unwanted side effects of the large-scale integration, the heat that is dissipated in the electronic system. How to avoid products malfunction because of electromagnetic interference.

#### Module I: Design Process and Its Fundamentals

Life Cycle of Electronic Products, Design and Development Process, Guidance for Product Planning, Design and Development, Technical Drawings, Circuit Diagrams, Computer-Aided Design (CAD), System Architecture and Protection Requirements, System Design Architecture, Electronic System Levels, System Protection.

#### Module II: Reliability Analysis

Calculation Principles, Exponential Distribution, Failure of Electronic Components, Failure of Electronic Systems, Reliability Analysis of Electronic Systems, Recommendations for Improving Reliability of Electronic Systems

#### Module III: Thermal Management and Cooling

Introduction—Terminology, Temperatures, and Power Dissipation, Calculation Principles, Heat Transfer, Methods to Increase Heat Transfer, Application Examples in Electronic Systems, Recommendations for Thermal Management of Electronic Systems

#### Module IV: Electromagnetic Compatibility (EMC)

Coupling Between System Components, Grounding Electronic Systems, Shielding from Fields, Electrostatic Discharge (ESD), Recommendations for EMC - Compliant Systems Design

## Module V: Recycling Requirements and Design for Environmental Compliance

Introduction—Motivation and the Circular Economy, Design and Development for Disassembly, Material Suitability in Design and Development, Recommendations for Environmentally Compliant Systems.

**Course Plan** (For 3 credit courses, the content can be for 40 hrs and for 2 credit courses, the content can be for 26 hrs. The audit course in third semester can have content for 30 hours).

| No  | Topic                                            | No. of   |

|-----|--------------------------------------------------|----------|

|     |                                                  | Lectures |

| 1   | Module I - Design Process and Its Fundamentals   |          |

| 1.1 | Design & Development process                     | 3        |

| 1.2 | System Architecture and Protection Requirements  | 3        |

| 1.3 | System Protection                                | 2        |

| 2   | Module II - Reliability Analysis                 | A        |

| 2.1 | Failure of Electronic Components                 | 3        |

| 2.2 | Failure of Electronic Systems                    | 3        |

| 2.3 | Reliability Analysis of Electronic Systems       | 2        |

| 3   | Module III - Thermal Management and Cooling      |          |

| 3.1 | Terminology, Temperatures, and Power Dissipation | 3        |

| 3.2 | Heat Transfer                                    | 3        |

| 3.3 | Enclosure                                        | 2        |

| 4   | Module IV - Electromagnetic Compatibility (EMC)  |          |

| 4.1 | Coupling Between System Components               | 2        |

| 4.2 | Electrostatic Discharge (ESD)                    | 2        |

| 4.3 | Grounding Electronic Systems                     | 2        |

| 4.4 | Shielding from Fields                            | 2        |

| 5   | Module V - Recycling Requirements and Design for |          |

|     | Environmental Compliance                         |          |

| 5.1 | Product Recycling in the Disposal Process        | 3        |

| 5.2 | Design and Development for Disassembly           | 3        |

| 5.3 | Material Suitability in Design and Development   | 2        |

#### **Text Books**

- 1. Fundamentals of Electronic Systems Design Jens Lienig, Hans Brümmer Springer Cham Publishers

- 2. Birolini, Reliability Engineering. Theory and Practice, 7th edition, Springer, 2014

- 3. R. Reemsburg, Thermal Design of Electronic Equipment (Electronics Handbook), CRC Press, 2000

- 4. Tecknit, Electromagnetic Compatibility Guide, 1998

#### **Reference Books**

- 1. A practical guide to EMC Engineering Levent Sevgi Artech House Publishers

- 2. The Electrical Engineering Handbook Series Richard C Dorf CRC Press

- 3. Designing Electronic Product Enclosures Tony Serksnis Springer Cham Publishers

- 4. Fundamentals of Electronic Circuit Design Hongshen Ma Wiley; 1st edition (May 21, 2002)

- 5. Recycling for Climate Protection, Report of the Fraunhofer Institute for Environmental, Safety, and Energy Technology UMSICHT, February 8, 2011. Online

at:http://www.alba.info/fileadmin/alba/pressemappe/recycling\_fuer\_den\_klimaschutz/110210\_CO2\_Studie\_ALBA\_Group\_final\_v4.pdf

# PROGRAM ELECTIVE I

Estd.

2014

| CODE      | COURSE NAME        | CATEGORY           | L | T | P | CREDIT |

|-----------|--------------------|--------------------|---|---|---|--------|

| 221EEC063 | EMBEDDED           | PROGRAM ELECTIVE 1 | 3 | 0 | 0 | 3      |

|           | <b>PROGRAMMING</b> |                    |   |   |   |        |

**Preamble:** The C Standards Committee created the Embedded C as a collection of language extensions for the C programming language to address commonality concerns that emerge with C extensions for various embedded systems. It's used to create microcontroller programming software Fixed-point arithmetic, named address spaces, and essential I/O hardware addressing are all characteristics not accessible in normal C. The course also covers object oriented programming using C++. The course will give an overview of Coding Standards For Compliance.

**Course Outcomes:** The COs shown are only indicative. For each course, there can be 4 to 6 COs.

After the completion of the course the student will be able to

| СО | Attain comprehensive understanding of fundamentals of C                |

|----|------------------------------------------------------------------------|

| 1  | Programming                                                            |

|    | (Cognitive knowledge level: <b>Understand</b> ).                       |

|    |                                                                        |

| СО | Attain comprehensive understanding of Embedded C                       |

| 2  | (Cognitive knowledge level: <b>Understand</b> ).                       |

| СО | Attain comprehensive understanding of Embedded Programming and         |

| 3  | development Tools                                                      |

|    | (Cognitive knowledge levels: <b>Understand, analyse, &amp;create</b> ) |

| СО | Attain comprehensive understanding of fundamentals of Comprehend       |

| 4  | the fundamentals of C++                                                |

|    | (Cognitive knowledge levels: <b>Understand, analyse, &amp;create</b> ) |

| СО | Attain comprehensive understanding of the state-of- art hardware       |

| 5  | and software tools for Embedded software development                   |

|    | (Cognitive knowledge levels: Understand, analyse, create &             |

|    | Evaluate).                                                             |

| СО | Attain comprehensive understanding of the Embedded Programming         |

| 6  | Coding standards & Concepts                                            |

|    | (Cognitive knowledge levels: <b>Understand &amp; Apply</b> )           |

|    |                                                                        |

| 7 r ·   | c                |         |           | 1      |         |          |

|---------|------------------|---------|-----------|--------|---------|----------|

| Manning | $\cap$ t         | COLLEGE | Olltcomes | 73711h | nrogram | outcomes |

| Mapping | $O_{\mathbf{I}}$ | course  | dateonics | AAICII | program | dateomes |

|      | PO 1 | PO 2   | PO 3   | PO 4 | PO 5  | PO 6  | PO 7 |

|------|------|--------|--------|------|-------|-------|------|

| CO 1 | 1    | 1      | -      | 3    | -     | -     | -    |

| CO 2 | -    | -      | -      | -    | 1     | 2     | -    |

| CO 3 | -    | -      | 2      | -    | 2     | -     | -    |

| CO 4 | -    | -      | 3      | -    | 2     | -     | -    |

| CO 5 | 2    | T -A 1 | 3 7-17 | 3    | 7 A-T | A + 1 | -    |

| CO 6 | 2    | -      | 71-71  | 3    | VAL.  | HIV   | -    |

#### Assessment Pattern

| Bloom's Category | End Semester |

|------------------|--------------|

|                  | Examination  |

| Apply            | 20           |

| Analyse          | 20           |

| Evaluate         | 10           |

| Create           | 10           |

#### Mark distribution

| Total<br>Marks | CIE | ESE | ESE<br>Duration |

|----------------|-----|-----|-----------------|

| 100            | 40  | 60  | 2.5 hours       |

#### Continuous Internal Evaluation Pattern: 40 Marks

Preparing a review article based on peer reviewed original publications (minimum 10 publications shall be referred) : 15 marks

Course based task/Seminar/Data collection and interpretation: 15 marks

Test paper, 1 no.: 10 marks Test paper shall include minimum 80% of the syllabus.

#### **End Semester Examination Pattern: 60 Marks**

The end semester examination will be conducted by the respective College. There will be two parts; Part A and Part B. Part A will contain 5 numerical/short answer questions with 1 question from each module, having 5 marks for each question (such questions shall be useful in the testing of knowledge, skills, comprehension, application, analysis, synthesis, evaluation and understanding of the students). Students should answer all questions. Part B will contain 7 questions (such questions shall be useful in

the testing of overall achievement and maturity of the students in a course, through long answer questions relating to theoretical/practical knowledge, derivations, problem solving and quantitative evaluation), with minimum one question from each module of which student should answer any five. Each question can carry 7 marks.

#### **Model Question paper**

## APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY MONTH & YEAR

| Course Code: Course Name: Embedded Programming |                                     |                                |                        |              |            |       |  |  |  |

|------------------------------------------------|-------------------------------------|--------------------------------|------------------------|--------------|------------|-------|--|--|--|

| 221                                            | TEC002                              | ADINI                          | 7.7                    | IZ A         | TAAA       |       |  |  |  |

| Tim                                            | Time: 2.5 Hours Maximum: 60 Marks   |                                |                        |              |            |       |  |  |  |

|                                                | PAR                                 | TA (Answer all                 | l questi               | ions)        | ÇAL        | Marks |  |  |  |

| 1                                              | Discuss about ty                    | pes of UML mod                 | eling.                 | SH           | Y          | 5     |  |  |  |

| 2                                              | What is Makefile                    | ? Discuss its usa              | age with               | n suitable   | examples.  | 5     |  |  |  |

| 3                                              | Illustrate the diff                 | erence between                 | C and                  | Embedded     | . C.       | 5     |  |  |  |

| 4                                              | Briefly explain the examples.       | e polymorphism                 | concep                 | ots with su  | itable     | 5     |  |  |  |

| 5                                              | Explain the MISF<br>Embedded softwa |                                |                        | elevance ir  | 1          | 5     |  |  |  |

|                                                | PART                                | B (Answer any f                | ive que                | estions)     |            | Marks |  |  |  |

| 6.                                             | What do you mea                     |                                |                        | rite the al  | gorithm to | 7     |  |  |  |

| 7.                                             | i. GNU profiler ii. GNU C Compil    | E                              | option:                | s            | 1          | 7     |  |  |  |

| 8.                                             | Write a C program                   | m to implement                 | singly l               | inked list   | 7          | 7     |  |  |  |

| 9.                                             | Explain function program.           | overloading with               | h the he               | elp of a sui | table C++  | 7     |  |  |  |

| 10                                             | Describe inherita                   | ince con <mark>cepts wi</mark> | th <mark>suit</mark> a | able C++ p   | rograms.   | 7     |  |  |  |

| 11                                             | Discuss the complete detail.        | pute bound opti                | misatio                | n techniqu   | les in     | 7     |  |  |  |

| 12                                             | Describe IEEE-7                     | 54 standard and                | l applic               | ations.      |            | 7     |  |  |  |

#### **Syllabus**

### Module1: Introduction to Programming & algorithms for problem solving

The Basic Model of Computation, Algorithms, Flow-charts, Programming Languages, Compilation, Linking and Loading, Testing and Debugging, Algorithms for Problem Solving:Decimal Base to Binary Base conversion, Reversing digits of an integer, GCD (Greatest Common Division), LCM etc., Use case diagrams and UML.

#### Module2: C Programming Basics