VL800 : Certificate Program on System Verilog and UVM

VL800 : Certificate Program on System Verilog and UVM

The course teaches how to apply System Verilog to do verification and verification architecture design. It teaches System Verilog's key concepts such as data types, RTL design, Interfaces, clocking, assertion-based verification, and classes. The course provides a number of code samples and examples to give students a better feel for the language. It equips students to design a high performance IC or VLSI chip by imparting knowledge of all aspects of digital design, from architecture, application algorithm to fabrication.

Skills Gained after completing this training, you will know how to:

- Describe the advantages and enhancements to SystemVerilog to support verification

- Define the new data types available in SystemVerilog

- Analyze and use the improvements to tasks and functions

- Discuss and use the various new verification building blocks available in SystemVerilog

- Describe object-oriented programming and create a class-based verification environment

- Explain the various methods for creating random data

- Create and utilize random data for generating stimulus to a DUT

- Identify how SystemVerilog enhances functional coverage for simulation verification

- Utilize assertions to quickly identify correct behavior in simulation

- Identify how the direct programming interface can be used with C/C++ in a verification environment.

- Understand the features and capabilities of the UVM environment for SystemVerilog

This course contains 2 modules. After completing the First module, the students have to do a 3 weeks project using any of the topics studied to earn the Certificate.

| VL800: Certificate Program on System Verilog and UVM | |||

| Module & Course Code | Module Name | Duration (Weeks) | |

| Module I | VL801 | System Verilog and UVM | 5 |

| Module II | VL802 | Project | 3 |

| First Selection List publication | 9th October 2018 |

| Counselling | 15th October 2018 |

| Class Starting | 16th October 2018 |

For more details like How to Apply, Placement, Hostel, etc please see the Course Calendar or Course Prospectus

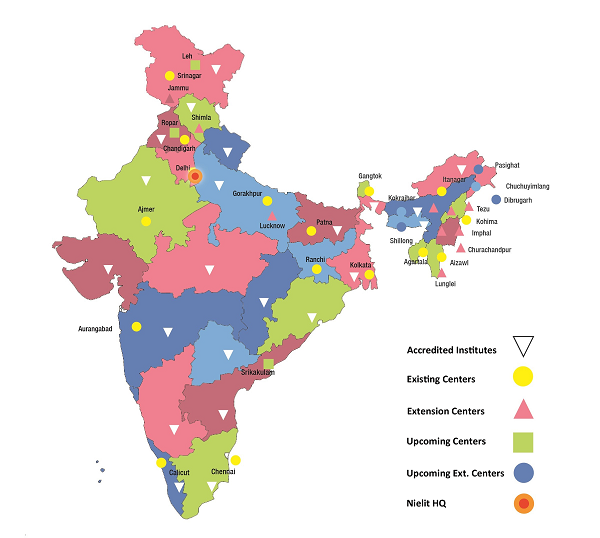

For more Information Contact the course coordinator Mr.Sreejeesh S.G , Email:sreejeesh@nielit.gov.in , Phone 0495 -2287266 (ext. 222). or WhatsApp # 9446711666

SystemVerilog is the first industry-standard language covering the requirements of both design and verification. It provides the benefits of broad capability in all areas of design and verification, with the advantage of a widely supported IEEE standard spanning project generations. It's a massive language that breaks down into three separate blocks; the design language, assertions, and the testbench language.

This course on System Verilog and UVM how to get started with using SV as a language in Verification Scenario. It covers the basics of SV syntax, explains verification mechanisms including working with arrays, classes, matrices etc.

Course Overview

♦ SystemVerilog modeling concepts

♦ Data types, declarations, syntax rules

♦ Procedural blocks and assignments

♦ Programming statements

♦ Operators and operation rules

♦ Compound data types and packages

♦ SystemVerilog interface ports

♦ Verification constructs and testbench interfaces

♦ Verification timing using clocking blocks

♦ Object Oriented testbenches

♦ Dynamic arrays and scoreboards

♦ Constrained random stimulus generation

♦ Functional coverage

♦ Synchronization (events, mailboxes, semaphores)

♦ Assertions overview

♦ UVM Environment Overview – One Case Study

- Project

Course fee is Rs 25,000/- including Service Tax.

ME/M-Tech/B.E/B.Tech/B.Sc/MSc/Engineering Graduates/PG in Electrical/Electronics/Electronics &Communication/Bio-Medical Engineering/Medical Electronics/Electronics & Instrumentation/Computer Science and allied branches.

Prerequisites:

Knowledge in verilog HDL, C, C++, OOPS Concepts.

Sreejeesh S.G